„OpenLS-DGF: Elastyczne i Otwarto-Źródłowe Narzędzie do Tworzenia Zbiorów Danych dla Zadań Uczenia Maszynowego w Syntezie Logiki”

Synteza logiki i jej rozwój z zastosowaniem uczenia maszynowego

Synteza logiki to kluczowy etap projektowania obwodów cyfrowych, który polega na przekształcaniu wysokopoziomowych opisów w szczegółowe projekty na poziomie bram. W ostatnich latach rozwój algorytmów uczenia maszynowego (ML) zrewolucjonizował wiele dziedzin, takich jak autonomiczne pojazdy, robotyka czy przetwarzanie języka naturalnego. Podobne podejście zaczęto stosować w syntezie logiki, co przynosi wymierne korzyści w takich obszarach jak optymalizacja logiki, mapowanie technologiczne czy formalna weryfikacja. Dzięki tym metodom można znacząco poprawić efektywność i jakość procesu syntezy logiki, czyniąc go szybszym i bardziej precyzyjnym. Jednak aby osiągnąć kolejne przełomy w tej dziedzinie, niezbędne są bardziej wiarygodne i uniwersalne zestawy danych.

—

Tradycyjne zestawy danych i ich ograniczenia

Tradycyjne benchmarki odegrały kluczową rolę w rozwoju narzędzi do projektowania układów elektronicznych (EDA), służąc jako podstawa do testowania, porównań i ulepszania technologii. Na ich podstawie powstawały zestawy danych, takie jak OpenABC-D, które były wykorzystywane w procesach syntezy logiki. Niestety, zestawy te były projektowane z myślą o konkretnych zadaniach, co ograniczało ich zastosowanie w innych obszarach uczenia maszynowego. Dodatkowo, nie zachowywały one pełnych informacji zawartych w plikach pośrednich, co utrudniało ich dalszą adaptację i rozwój w odpowiedzi na nowe wyzwania.

—

OpenLS-DGF – nowa era w syntezie logiki

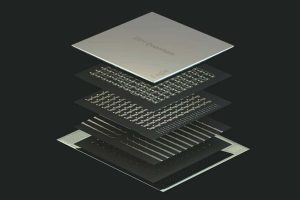

Aby przezwyciężyć wspomniane ograniczenia, zespół badaczy z Chin opracował framework OpenLS-DGF – adaptacyjny system generowania zestawów danych dla syntezy logiki, stworzony z myślą o wspieraniu różnorodnych zadań związanych z uczeniem maszynowym. Framework ten obejmuje trzy kluczowe etapy procesu syntezy logiki: reprezentację Boole’a, optymalizację logiki oraz mapowanie technologiczne.

Proces generowania danych w ramach OpenLS-DGF składa się z siedmiu kroków, począwszy od generowania surowych plików projektowych, aż po pakowanie danych w formacie PyTorch. Pierwsze etapy obejmują wstępne przetwarzanie projektów wejściowych, które są przekształcane w obwody zoptymalizowane w formacie AIG (And-Inverter Graphs). Kolejne kroki obejmują generowanie pośrednich obwodów logicznych, w tym mapowanie technologiczne oraz projektowanie fizyczne. Ostatecznie, wszystkie dane są pakowane w formacie PyTorch przy użyciu specjalnego silnika Circuit, co ułatwia ich zarządzanie i wykorzystanie w badaniach.

—

Proces generowania danych i przechowywania informacji

Proces generowania zestawów danych w OpenLS-DGF jest niezwykle kompleksowy. Projekty wejściowe są najpierw standaryzowane do formatu GTG, a następnie przekształcane w zoptymalizowane obwody AIG. Generowane są różnorodne warianty obwodów w sześciu formatach, które są odpowiednie zarówno dla projektów ASIC, jak i FPGA. Wyniki są analizowane pod kątem wydajności, a dane końcowe są uporządkowane w formie plików PyTorch, co umożliwia ich łatwe wykorzystanie i walidację.

Silnik Circuit odgrywa kluczową rolę w procesie przekształcania surowych plików w gotowe zestawy danych. Dzięki klasie „Circuit” możliwe jest definiowanie węzłów z atrybutami, takimi jak typ, nazwa czy połączenia. Silnik ten wspiera również symulacje oraz kompatybilność z frameworkami ML, takimi jak Torch Geometry. Pliki w formatach Verilog i GraphML są wczytywane za pomocą NetworkX, co umożliwia tworzenie dobrze zorganizowanych struktur grafowych.

—

Zestaw danych OpenLS-D-v1 – nowe standardy w badaniach

Zestaw danych OpenLS-D-v1 został stworzony na podstawie różnorodnych projektów benchmarkowych, takich jak IWLS i OpenCores. Obejmuje on szeroką gamę obwodów kombinacyjnych, w tym sieci Boole’a z wieloma wejściami i wyjściami. Wśród obwodów znajdują się zarówno układy arytmetyczne, jak i kontrolne oraz rdzenie IP. Dane są analizowane za pomocą kombinacji cech heurystycznych i reprezentacji grafowych Graph2Vec.

Zestaw OpenLS-D-v1 zawiera imponującą liczbę 966 000 obwodów, które zostały podzielone na 46 projektów. Każdy z projektów obejmuje różne typy sieci Boole’a oraz siatki dla zastosowań ASIC i FPGA. W porównaniu do zestawu OpenABC-D, OpenLS-D-v1 oferuje znacznie większą różnorodność, co czyni go bardziej reprezentatywnym dla zadań związanych z uczeniem maszynowym.

—

Wyniki eksperymentów i przyszłość frameworka

Eksperymenty przeprowadzono na dziesięciu projektach z zestawu OpenLS-D-v1, takich jak „ctrl”, „router” czy „int2float”. Procesy treningowe wykorzystywały około 120 000 par danych do rankingowania, osiągając wysoki poziom dokładności predykcji. W przypadku przewidywania jakości wyników (QoR) uzyskano bardzo niskie błędy procentowe, takie jak 4,31% dla GraphSAGE, 4,43% dla GINConv oraz 5,09% dla GCNConv. W obszarze predykcji probabilistycznej metody takie jak DeepGate zmniejszyły średnie błędy predykcji o 75%, przy jednoczesnym skróceniu czasu obliczeń aż 56,89× w porównaniu do GraphSAGE.

—

Podsumowanie i perspektywy

Framework OpenLS-DGF stanowi ogromny krok naprzód w dziedzinie syntezy logiki, oferując wsparcie dla różnorodnych zadań ML i wprowadzając ustandaryzowany proces generowania danych. Zestaw OpenLS-D-v1 dodatkowo wzmacnia jego potencjał, dostarczając naukowcom solidnej bazy do przyszłych badań i innowacji. Wyniki dotychczasowych eksperymentów potwierdzają skuteczność i wszechstronność tego rozwiązania.

W przyszłości planowane są dalsze usprawnienia procesu generowania danych, a także tworzenie benchmarków dostosowanych do specyficznych zadań związanych z uczeniem maszynowym w syntezie logiki. To otwiera drzwi do jeszcze bardziej precyzyjnych i zaawansowanych zastosowań w tej dynamicznie rozwijającej się dziedzinie.